“TI集成电路74HC165逻辑IC”参数说明

| 型号: | 74HC165 | 产量: | 50000/月 |

“TI集成电路74HC165逻辑IC”详细介绍

74HC165是一款高速CMOS器件,74HC165遵循JEDEC标准no.7A.74HC165引脚兼容低功耗肖特基TTL(LSTTL)系列。

74HC165是8位并行读取或串行输入移位寄存器,可在末级得到互斥的串行输出(Q7和Q7),当并行读取(PL)输入为低时,从D0到D7口输入的并行数据将被异步地读取进寄存器内。

而当PL为高时,数据将从DS输入端串行进入寄存器,在每个时钟脉冲的上升沿向右移动一位(Q0→Q1→Q2,等等)。利用这种特性,只要把Q7输出绑定到下一级的DS输入,即可实现并转串扩展。

74HC165的时钟输入是一个“门控或”结构,允许其中一个输入端作为低有效时钟使能(CE)输入。CP和CE的引脚分配是独立的并且在必要时,为了布线的方便可以互换。只有在CP为高时,才允许CE由低转高。在PL上升沿来临之前,不论是CP还是CE,都应当置高,以防止数据在PL的活动状态发生位移。

74HC165 基本参数

电压 2.0~6.0V

驱动电流+/-5.2 mA

传输延迟 16 ns@5V

74HC165 其他特性

最高频率 56 MHz

逻辑电平 CMOS

功耗考量低功耗或电池供电应用

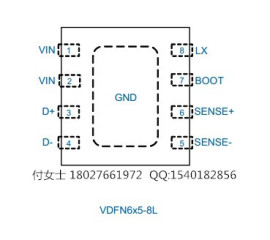

74HC165 封装与引脚

SO16,SSOP16,DIP16,TSSOP16

74HC165 特性

异步8位并行读取

同步串行输入

兼容JEDEC标准no.7A

ESD保护

HBM EIA/JESD22-A114E超过2000 V

MM EIA/JESD22-A115-A超过200 V

温度范围

-40~+85℃

-40~+125℃

74HC165是8位并行读取或串行输入移位寄存器,可在末级得到互斥的串行输出(Q7和Q7),当并行读取(PL)输入为低时,从D0到D7口输入的并行数据将被异步地读取进寄存器内。

而当PL为高时,数据将从DS输入端串行进入寄存器,在每个时钟脉冲的上升沿向右移动一位(Q0→Q1→Q2,等等)。利用这种特性,只要把Q7输出绑定到下一级的DS输入,即可实现并转串扩展。

74HC165的时钟输入是一个“门控或”结构,允许其中一个输入端作为低有效时钟使能(CE)输入。CP和CE的引脚分配是独立的并且在必要时,为了布线的方便可以互换。只有在CP为高时,才允许CE由低转高。在PL上升沿来临之前,不论是CP还是CE,都应当置高,以防止数据在PL的活动状态发生位移。

74HC165 基本参数

电压 2.0~6.0V

驱动电流+/-5.2 mA

传输延迟 16 ns@5V

74HC165 其他特性

最高频率 56 MHz

逻辑电平 CMOS

功耗考量低功耗或电池供电应用

74HC165 封装与引脚

SO16,SSOP16,DIP16,TSSOP16

74HC165 特性

异步8位并行读取

同步串行输入

兼容JEDEC标准no.7A

ESD保护

HBM EIA/JESD22-A114E超过2000 V

MM EIA/JESD22-A115-A超过200 V

温度范围

-40~+85℃

-40~+125℃

通过认证

通过认证